TMS320C6657CZHA IC DSP FIX/FLOAT POINT 625FCBGA

Produit Parameter

Beschreiwung

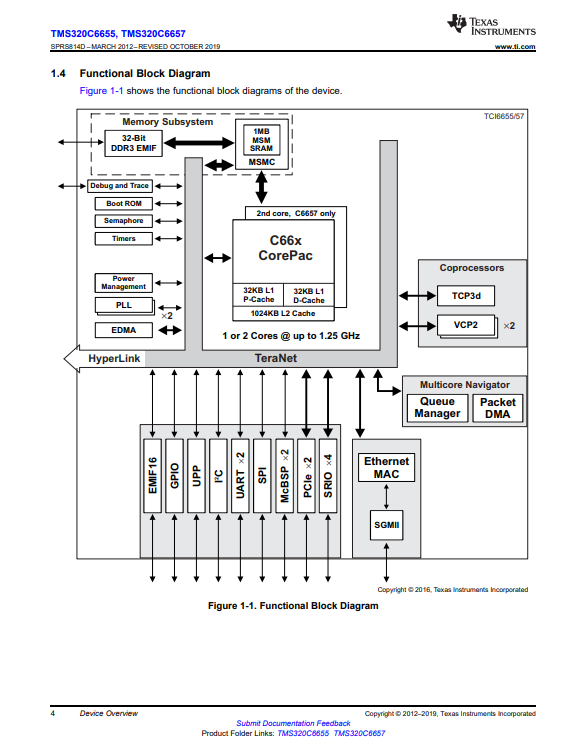

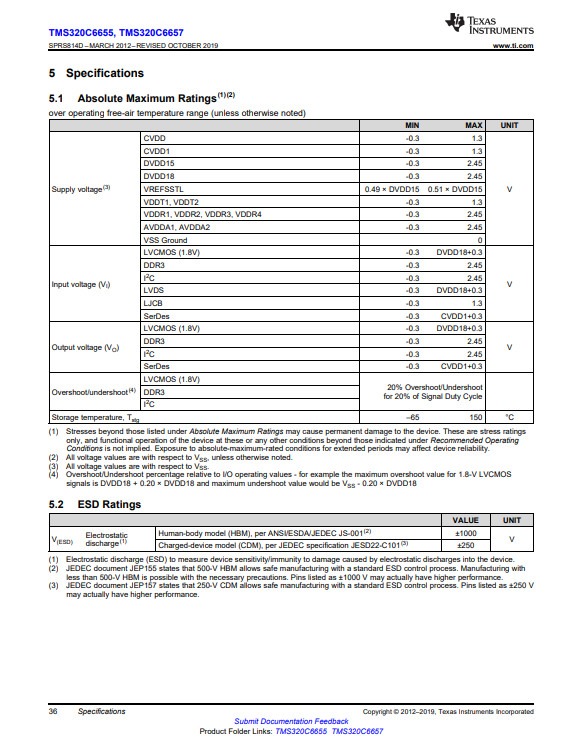

TI's KeyStone Architektur bitt eng programméierbar Plattform déi verschidde Subsystemer integréiert (C66x Cores, Memory Subsystem, Peripherieger a Beschleuniger) a benotzt verschidden innovativ Komponenten an Techniken fir d'Intragerät an d'Interdevice Kommunikatioun ze maximéieren, déi déi verschidde DSP Ressourcen effizient an nahtlos operéiere loossen.Zentral zu dëser Architektur sinn Schlësselkomponenten wéi Multicore Navigator, déi et effizient Datemanagement tëscht de verschiddenen Apparatkomponenten erlaabt.Den TeraNet ass en net-blockéierende Schaltstoff deen séier a streitfräi intern Datenbewegung erméiglecht.De Multicore Shared Memory Controller erlaabt Zougang zu gedeelt an extern Erënnerung direkt ouni aus Schaltstoffkapazitéit ze zéien.Fir fixe Punkt Benotzung huet de C66x Kär 4 × d'Multiplizéieren accumuléieren (MAC) Kapazitéit vun C64x+ Cores.Zousätzlech integréiert de C66x Kär Floating-Point Kapazitéit an d'per-Core raw computational Leeschtung ass eng industrieféierend 40 GMACS pro Kär an 20 GFLOPS pro Kär (@1.25 GHz Betribsfrequenz).De C66x Kär kann 8 eenzeg Präzisioun Floating-Point MAC Operatiounen pro Zyklus ausféieren a kann duebel- a gemëschtpräzis Operatiounen ausféieren an ass IEEE 754 konform.De C66x Kär enthält 90 nei Instruktiounen (am Verglach zum C64x+ Kär) gezielt fir Floating Point a Vector Mathematik orientéierter Veraarbechtung.Dës Verbesserunge ginn erheblech Leeschtungsverbesserungen a populäre DSP Kernelen, déi an der Signalveraarbechtung, mathematesch a Bildacquisitiounsfunktiounen benotzt ginn.De C66x Kär ass réckgängeg Code-kompatibel mat der viregter Generatioun C6000 Fixed- a Floating Point DSP Cores vun TI, garantéiert Softwareportabilitéit a verkierzte Softwareentwécklungszyklen fir Uwendungen, déi op méi séier Hardware migréieren.D'C665x DSP integréiert eng grouss Quantitéit vun On-Chip Erënnerung.Zousätzlech zu 32KB vum L1 Programm an Datekache, kann 1024KB vun dedizéierten Erënnerung als mapéiert RAM oder Cache konfiguréiert ginn.Den Apparat integréiert och 1024KB Multicore Shared Memory dat als gemeinsame L2 SRAM an / oder gemeinsame L3 SRAM benotzt ka ginn.All L2 Erënnerungen enthalen Feelererkennung a Feelerkorrektur.Fir séier Zougang zu externen Erënnerung, enthält dësen Apparat eng 32-bëssen DDR-3 extern Erënnerung Interface (EMIF) Lafen mat engem Taux vun 1333 MHz an huet ECC DRAM Ënnerstëtzung.

| Spezifikatioune: | |

| Attribut | Wäert |

| Kategorie | Integréiert Circuits (ICs) |

| Embedded - DSP (Digital Signal Prozessoren) | |

| Mfr | Texas Instrumenter |

| Serie | TMS320C66x Ubidder |

| Package | Schacht |

| Deel Status | Aktiv |

| Typ | Fixed / Floating Point |

| Interface | DDR3, EBI/EMI, Ethernet, McBSP, PCIe, I²C, SPI, UART, UPP |

| Auer Taux | 1 ghz |

| Net-flüchteg Erënnerung | ROM (128 kB) |

| On-Chip RAM | 2,06 MB |

| Spannung - ech / O | 1,0 V, 1,5 V, 1,8 V |

| Spannung - Kär | 1,00 V |

| Operatioun Temperatur | -40°C ~ 100°C (TC) |

| Montéierung Typ | Surface Mount |

| Package / Fall | 625-BFBGA, FCBGA |

| Fournisseur Apparat Package | 625-FCBGA (21x21) |

| Basis Produit Zuel | TMS320 |

ZesummenhangPRODUITEN

-

Tel

-

E-Mail

-

skype

-

whatsapp

whatsapp